Tesira Compiler Errors

A brief explanation of how the compiler works.

The compilation process can be divided into the "Allocation" and the "Assignment" stages, followed by the delay equalization of the whole layout.

Allocation

The first task performed by the compiler is to combine the blocks contained in a partition into groups and distribute them among the available Tesira devices. After the groups are built, it will analyze all feasible combinations and select the most optimal one. This process will be subsequently applied to all the partitions in the layout one by one, and it is in this stage where logical units will be added or removed in the equipment table if necessary (given the "Add devices" option in "Application Settings" is activated). It is important to understand that the groups are created so it can be viable to calculate a manageable number of combinations, and the individual blocks inside the groups are the ones being allocated to physical or logical units.

Assignment

In this stage, the blocks are assigned to a specific DSP inside the allocated unit. The DSP resources required by each block play an important role in the distribution of the blocks since it determines the number of cards needed by each unit. During the assignment phase, the compiler sets aside some DSP resources that will be needed during the next stage: Delay Equalization.

Delay equalization

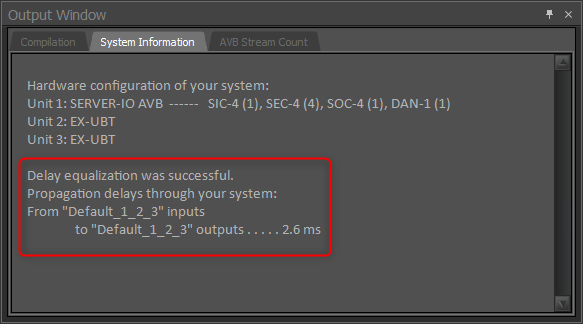

The last endeavor of the compiler is to time align all inputs of input blocks (i.e. analog vs. AEC inputs, pre-matrix) and all outputs of output blocks (i.e. latency differences generated by post-matrix processing). Once again, new groups are created (also called delay blocks), but this time under the hood and they´re not visible until the process is completed and it´s shown in the Output window - System Information tab:

An important note about the compilation process is that it is executed to one partition at a time, which means that the compiler will calculate DSP allocation and assignment on a per-partition basis. If a more cost-effective solution is desired, the "Perform Global Optimization" option in the "Compilation" menu will re-analyze the already compiled layout and look for a better option.

Tesira Software offers different options to analyze the behavior of the compiler and how the groups are distributed within a specific file. The Compilation tab under the Output window shows: information on allocation, assignment, groups, and blocks. Errors are also displayed here.

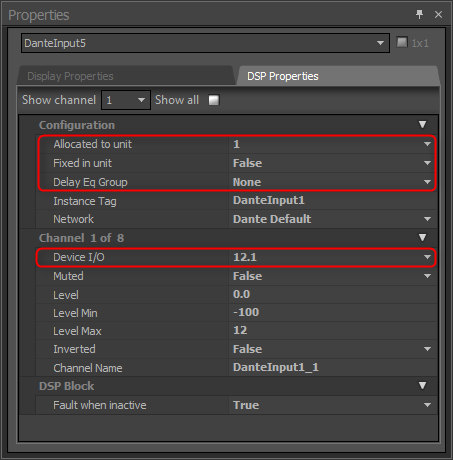

The Properties ducking window shows unit allocation, indicates if it´s fixed to specific hardware, the Delay Eq Group, and the DSP card it´s assigned to.

The DSP Block Information Field shows when the Display group assignment is selected. The number on the upper left corner of the block will be displayed in white on a black background, indicating the group of which that block is a member.

Compiler errors

"The number of feasible combinations exceeded the limit of 2000000"

Cause:

-

Too many AEC or digital I/O blocks in the file will force the compiler to create an excessive amount of groups and (hidden) delay blocks to time align I/Os in the system.

Solution:

-

Reduce the number of blocks by grouping the digital inputs into multi-channel blocks.

-

Reduce the number of possible combinations by pre-assigning I/O blocks to their specific device class in the Equipment Type dialog box of the Initialization window.

"There is no complete signal path from an input to an output in the layout"

Cause:

-

No signal path is connected from an input block to an output block.

Solution:

-

Complete at least one signal path by connecting one input block to one output block.

Cause:

-

Single channel AEC reference block (pass-through) is not terminated.

Solution:

-

Terminate the single channel AEC reference signal path by connecting a finishing (i.e. output or signal present block) block to its output.

"Can´t fit in group"

Cause:

-

The limit of I/O channels has been surpassed on the configuration.

-

Audio signal is being routed to incongruent devices (i.e. AVB being sent to a Dante device).

-

A physical device has been fixed and it can´t satisfy the I/O requirements of the file.

-

A device has been fixed that cannot satisfy the DSP requirement. This can be the result of fixed in unit blocks, or when a file has already been sent to physical hardware, extracted and edited.

Solution:

-

Reduce the number of channels or change to another media type.

-

Carefully look for interconnected blocks allocated to mismatching devices.

-

Change the partition compilation order in the "Set Partition Compilation Order" in the System > Compilation dropdown menu to avoid the compiler adding new hardware.

-

Arrange the partitions tabs according to their number of I/O requirements.

"Can’t find a solution…"

Cause:

-

A partition contains a large quantity of I/O blocks, leading to an excessive number of groups and their combinations.

Solution:

-

Merge smaller I/O blocks into bigger ones (be mindful of the consequences on hardware allocation).

-

Split the layout into smaller partitions.

"No solution to the allocation problem could be found" or it´s taking an unacceptable amount of time to find an optimal configuration

Cause:

-

DSP resources are over in a system that is already allocated to physical devices.

-

A connection between two or more partitions has blocks allocated to different devices.

Solution:

- Stop the process by clicking "Accept", the file will compile with the best solution found at that point.

- Allocate blocks fixed to physical devices, paying special attention to big I/O blocks.

- Separate large partitions into smaller ones.

- Confirm that connections between partitions are allocated to the same device.

"Device Internal Software Error (m)"

Cause:

- Tesira Software lost network communication with the unit while uploading a file or upgrading the firmware and the DSP is running from the main partition.

- Failed firmware upgrade.

Solution:

- Clear the configuration and upload the file again.

- Power cycle or factory reset the device and attempt the firmware upgrade again.

"Device Internal Software Error (r)"

Cause:

- Tesira Software lost network communication with the unit while uploading a file or upgrading the firmware and the DSP is running from the recovery partition.

- Failed firmware upgrade.

Solution:

- Factory reset the device and attempt a firmware upgrade. If the error persists, contact Biamp support for assistance.